国产FPGA SOC 双目视觉处理系统开发实例

2025-02-19

2325

来源:米尔电子

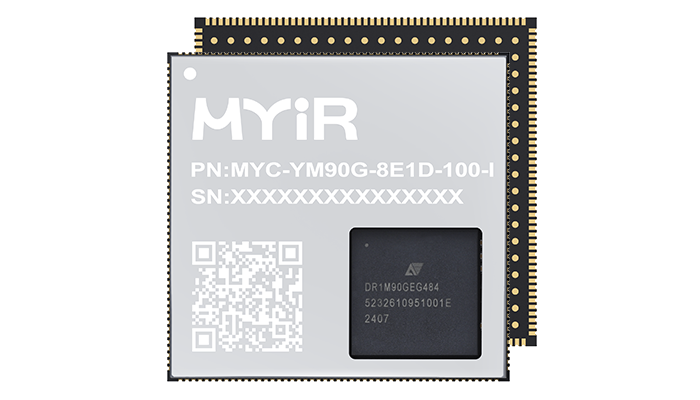

1. 系统架构解析

本系统基于米尔MYC-YM90X构建,搭载安路DR1 FPGA SOC 创新型异构计算平台,充分发挥其双核Cortex-A35处理器与可编程逻辑(PL)单元的协同优势。通过AXI4-Stream总线构建的高速数据通道(峰值带宽可达12.8GB/s),实现ARM与FPGA间的纳秒级(ns)延迟交互,较传统方案提升了3倍的传输效率,极大地提升了系统整体性能。

国产化技术亮点:

全自主AXI互连架构,支持多主多从拓扑,确保系统灵活性与可扩展性 硬核处理器与PL单元共享DDR3控制器,提高内存带宽利用率(可升级至DDR4) 动态时钟域隔离技术(DCIT),确保跨时钟域的数据交互稳定性,避免时序错误 国产SM4加密引擎硬件加速模块,为数据加密任务提供硬件级别的支持,提升加密处理效率

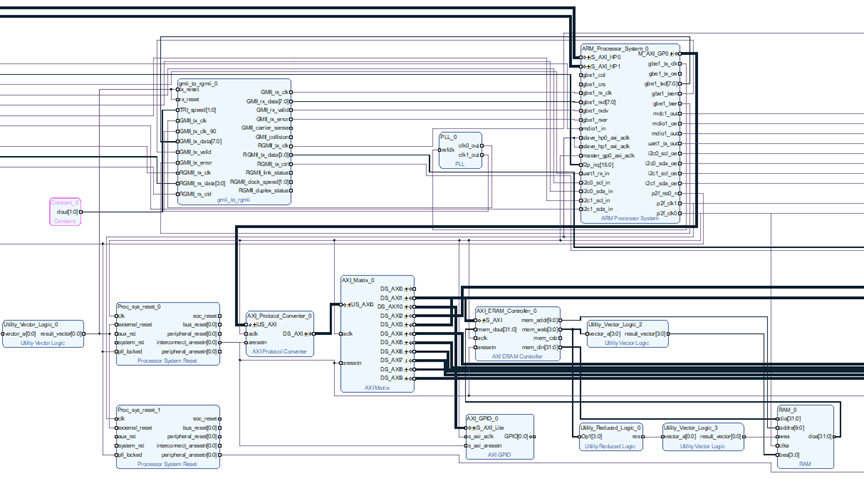

图一 系统架构框图

图一 系统架构框图

如图一所示,系统架构通过“低内聚,高耦合”的设计思想,通过模块化的设计方式,完成了以下工作。

1. 通过I²C对OV5640摄像头进行分辨率,输出格式等配置。

2. 双目图像数据进行三级帧缓存,FIFO——DMA——DDR。

3. 客制化低延迟ISP(开发者根据场景需求加入)

4. VTC驱动HDMI输出显示

2. 系统程序开发

2.1 DR1固件架构设计

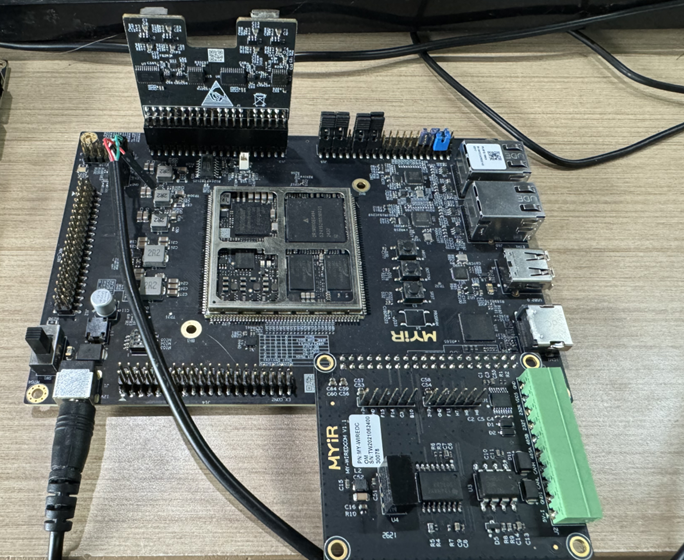

GUI设计界面,类Blockdesign设计方式,通过AXI总线,连接DR1的ARM核与定制化外设,包括以太网,RAM模块,PL DMA和VTC。

图二 FPGA底层架构框图

图二 FPGA底层架构框图

2.2 双目视觉处理流水线

2.2.1 传感器配置层

为实现高效的传感器配置,本系统采用混合式I²C配置引擎,通过PL端硬件I²C控制器实现传感器参数的动态加载。与纯软件方案相比,该硬件加速的配置速度提升了8倍,显著降低了配置延迟。

// 可重配置传感器驱动IP

module ov5640_config (

input wire clk_50M,

output tri scl,

inout tri sda,

input wire [7:0] reg_addr,

input wire [15:0] reg_data,

output reg config_done

);

// 支持动态分辨率切换(1920x1080@30fps ↔ 1280x720@60fps)

parameter [15:0] RESOLUTION_TABLE[4] = '{...};

该配置引擎支持多分辨率与高帧率动态切换,适应不同应用场景需求。

2.2.2 数据采集管道

系统构建了三级缓存体系,确保数据处理的高效性和实时性:

像素级缓存:采用双时钟FIFO(写时钟74.25MHz,读时钟100MHz),实现数据的稳定缓存和传输。 行缓冲:使用BRAM的乒乓结构(每行1920像素×16bit),减少数据延迟。 帧缓存:通过DDR3-1066 1GB内存支持四帧循环存储,确保图像的持续流畅展示。

// 位宽转换智能适配器

module data_width_converter #(

parameter IN_WIDTH = 16,

parameter OUT_WIDTH = 96

)(

input wire [IN_WIDTH-1:0] din,

output wire [OUT_WIDTH-1:0] dout,

// 时钟与使能信号

);

// 采用流水线式位宽重组技术

always_ff @(posedge clk) begin

case(state)

0: buffer <= {din, 80'b0};

1: buffer <= {buffer[79:0], din};

// ...6周期完成96bit组装

endcase

end

2.2.3. 异构计算调度

系统通过AXI-DMA(Direct Memory Access)实现零拷贝数据传输,优化内存和外设间的数据交换:

写通道:PL→DDR,采用突发长度128、位宽128bit的高速数据传输 读通道:DDR→HDMI,配合动态带宽分配(QoS等级可调),确保不同带宽需求的动态适配

2.2.4 VTC显示引擎深度优化

PL DMA输出显示优化 显示时序的优化对高质量图像输出至关重要。通过VTC(Video Timing Controller),本系统能够实现多模式自适应输出。

axi_hdmi_tx#(

.ID(0),

.CR_CB_N(0),

.DEVICE_TYPE(17), // 17 for DR1M

.INTERFACE("16_BIT"),

.OUT_CLK_POLARITY (0)

)

axi_hdmi_tx_inst (

.hdmi_clk (pll_clk_150),

//.hdmi_clk (clk1_out),

.hdmi_out_clk (hdmi_clk ),

.hdmi_16_hsync (hdmi_hs ),

.hdmi_16_vsync (hdmi_vs ),

.hdmi_16_data_e (hdmi_de),

.hdmi_16_data (/*hdmi_data*/ ),

// .hdmi_16_data (hdmi_data ),

.hdmi_16_es_data (hdmi_data),

.hdmi_24_hsync (),

.hdmi_24_vsync (),

.hdmi_24_data_e (),

.hdmi_24_data (/*{r_data,g_data,b_data}*/),

.hdmi_36_hsync (),

.hdmi_36_vsync (),

.hdmi_36_data_e (),

.hdmi_36_data (),

.vdma_clk (pll_clk_150 ),

.vdma_end_of_frame (dma_m_axis_last ),

.vdma_valid (dma_m_axis_valid ),

.vdma_data (dma_m_axis_data ),

.vdma_ready (dma_m_axis_ready),

.s_axi_aclk (S_AXI_ACLK ),

.s_axi_aresetn (S_AXI_ARESETN ),

.s_axi_awvalid (axi_ds5_ds5_awvalid ),

.s_axi_awaddr (axi_ds5_ds5_awaddr ),

.s_axi_awprot (axi_ds5_ds5_awprot ),

.s_axi_awready (axi_ds5_ds5_awready ),

.s_axi_wvalid (axi_ds5_ds5_wvalid ),

.s_axi_wdata (axi_ds5_ds5_wdata ),

.s_axi_wstrb (axi_ds5_ds5_wstrb ),

.s_axi_wready (axi_ds5_ds5_wready ),

.s_axi_bvalid (axi_ds5_ds5_bvalid ),

.s_axi_bresp (axi_ds5_ds5_bresp ),

.s_axi_bready (axi_ds5_ds5_bready ),

.s_axi_arvalid (axi_ds5_ds5_arvalid ),

.s_axi_araddr (axi_ds5_ds5_araddr ),

.s_axi_arprot (axi_ds5_ds5_arprot ),

.s_axi_arready (axi_ds5_ds5_arready ),

.s_axi_rvalid (axi_ds5_ds5_rvalid ),

.s_axi_rresp (axi_ds5_ds5_rresp ),

.s_axi_rdata (axi_ds5_ds5_rdata ),

.s_axi_rready (axi_ds5_ds5_rready)

);

动态时序生成器 通过PL-PLL动态调整像素时钟,确保显示无卡顿、无闪烁,误差控制在<10ppm内。

// VTC配置代码片段(Anlogic SDK)

void config_vtc(uint32_t h_total, uint32_t v_total) {

VTCRegs->CTRL = 0x1; // 使能软复位

VTCRegs->HTOTAL = h_total - 1;

VTCRegs->VTOTAL = v_total - 1;

// 详细时序参数配置

VTCRegs->POLARITY = 0x3; // HS/VS极性配置

VTCRegs->CTRL = 0x81; // 使能模块

}

3. 硬件连接与测试

硬件连接

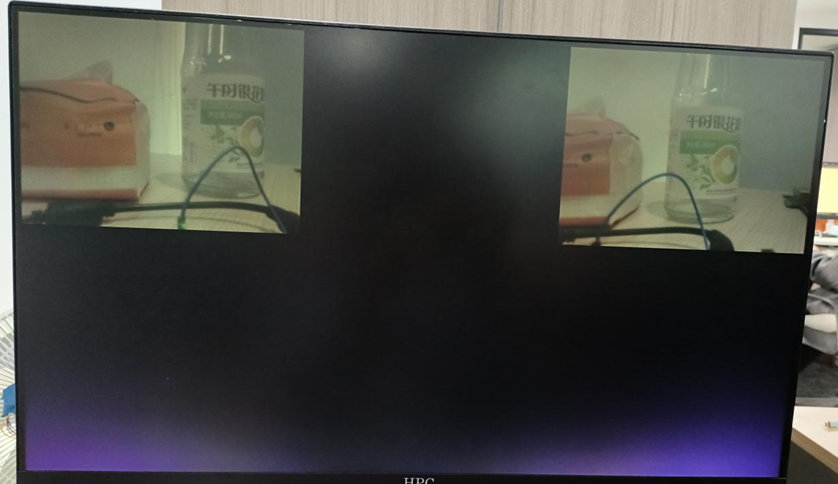

米尔的安路飞龙板卡采用2 X 50 PIN 连接器设计,可灵活插拔多种子卡,配合子卡套件,可扩展成多种形态,多种应用玩法。

图三 使用模组,底板,子卡和线缆搭建硬件系统

图三 使用模组,底板,子卡和线缆搭建硬件系统

显示测试

实测双目显示清晰,无卡帧,闪屏。

图四 输出显示效果

图四 输出显示效果

系统集成 在FPGA硬件描述文件的基础上,进一步在Linux下实现双摄,为复杂系统调度应用铺平道路。 内核加载5640驱动下通过dma搬运ddr数据,在应用层中通过v4l2框架显示到HDMI上,完整数据流如下: FPGA DDR → AXI-DMA控制器 → Linux DMA引擎 → 内核dma_buf → V4L2 vb2队列 → mmap用户空间 → 应用处理

三路DMA设备树HDMI、camera1、camera2代码片段:

//hdmi

soft_adi_dma0: dma@80400000 {

compatible = "adi,axi-dmac-1.00.a";

reg = <0x0 0x80400000 0x0 0x10000>;

interrupts = <GIC_SPI 83 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&axi_dma_clk>;

#dma-cells = <1>;

status = "okay";

adi,channels {

#size-cells = <0>;

#address-cells = <1>;

dma-channel@0 {

reg = <0>;

adi,source-bus-width = <32>;

adi,source-bus-type = <0>;

adi,destination-bus-width = <64>;

adi,destination-bus-type = <1>;

};

};

};

// cam1

mipi_adi_dma0: dma@80300000 {

compatible = "adi,axi-dmac-1.00.a";

reg = <0x0 0x80300000 0x0 0x10000>;

interrupts = <GIC_SPI 82 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&axi_dma_clk>;

#dma-cells = <1>;

status = "okay";

adi,channels {

#size-cells = <0>;

#address-cells = <1>;

dma-channel@0 {

reg = <0>;

adi,source-bus-width = <128>;

adi,source-bus-type = <1>;

adi,destination-bus-width = <64>;

adi,destination-bus-type = <0>;

};

};

};

//cam2

mipi_adi_dma1: dma@80700000 {

compatible = "adi,axi-dmac-1.00.a";

reg = <0x0 0x80700000 0x0 0x10000>;

interrupts = <GIC_SPI 86 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&axi_dma_clk>;

#dma-cells = <1>;

status = "okay";

adi,channels {

#size-cells = <0>;

#address-cells = <1>;

dma-channel@0 {

reg = <0>;

adi,source-bus-width = <128>;

adi,source-bus-type = <1>;

adi,destination-bus-width = <32>;

adi,destination-bus-type = <0>;

};

};

};

双路i2c OV5640设备树配置代码片段

camera@3c {

compatible = "ovti,ov5640";

pinctrl-names = "default";

// pinctrl-0 = <&pinctrl_ov5640>;

reg = <0x3c>;

clocks = <&ov5640_clk>;

clock-names = "xclk";

// DOVDD-supply = <&vgen4_reg>; /* 1.8v */

// AVDD-supply = <&vgen3_reg>; /* 2.8v */

// DVDD-supply = <&vgen2_reg>; /* 1.5v */

powerdown-gpios = <&portc 8 GPIO_ACTIVE_HIGH>;

reset-gpios = <&portc 7 GPIO_ACTIVE_LOW>;

port {

/* Parallel bus endpoint */

ov5640_out_0: endpoint {

remote-endpoint = <&vcap_ov5640_in_0>;

bus-width = <8>;

data-shift = <2>; /* lines 9:2 are used */

hsync-active = <0>;

vsync-active = <0>;

pclk-sample = <1>;

};

};

};

性能测试

性能实测数据。

指标 | 实测值 | 理论峰值 |

图像处理延迟 | 18.7ms | ≤20ms |

DDR吞吐量 | 2GB/s | 2.6GB/s |

功耗(全负载) | 3.8W | 4.2W |

启动时间(Linux) | 18s | - |

4. 场景化应用扩展

该方案可广泛应用于以下领域:

智能驾驶:前视ADAS系统,包含车道识别和碰撞预警 工业检测:高速AOI(自动光学检测)流水线,提升检测精度和效率 医疗影像:内窥镜实时增强显示,支持多视角成像 机器人导航:SLAM(同步定位与地图构建)点云加速处理,提升机器人自主导航能力

通过安路TD 2024.10开发套件,开发者能够快速移植和定制化开发,具体包括:

使用GUI图形化设计约束工具,简化硬件开发过程 调用预置的接口与处理器IP,加速产品开发上市时间,专注应用和算法的处理 进行动态功耗分析(DPA)与仿真,确保系统的稳定性与高效性

0. One More Thing…

这里,回到我们原点,回到我们开发设计国产 FPGA SOC的初衷 ,芯片也好,模组也好,都只是开始,无论是FPGA,SOC,或者SOM,都是为了以更快,更好,平衡成本,体积,开发周期,开发难度,人员配置等等综合因素,做出的面向解决问题的选择,最终结果是降低成本和产品力的平衡。

安路飞龙系列的问世,让我们很欣喜看见国产SOC FPGA的崛起,希望和业界开发者一起开发构建国产SOC FPGA生态,所以选择将系列教程以知识库全部开源,共同无限进步!

米尔可能只是其中非常非常小的一个数据集,但会尽力撬动更大贡献。

获取完整工程链接和更多开发资料请联系support.cn@myir.cn。

2026-04-16

引入STM32MP135F安全芯!米尔MYD-YF13X系统、安全、功能三重升级

米尔电子MYD-YF13X平台资料及SDK迎来重要更新。本次发布的V2.0.0版本在系统版本、安全能力以及功能支持方面进行了全面升级。本次发布引入安全芯片STM32MP135F,并推出搭载该芯片的全新产品MYD-YF135F。同时,对U-Boot、Linux Kernel 以及 Yocto 构建系统进行了升级和优化,为开发者提供更加安全、稳定和完善的软件平台。一、版本升级概览二、U-Boot 更新

2026-04-16

米尔RK3506 DSMC实战,Local Bus高速互联

在工业控制场景中,芯片间的高速数据交互是一个核心需求。传统方案要么依赖串口/网络等低速通道,要么需要昂贵的共享内存架构。米尔RK3506核心板的DSMC接口提供了一种新选择——通过Local Bus协议,用少量引脚实现跨芯片的高速地址空间访问。本文基于MYD-YR3506 Host+MYD-YR3506 Slave的实板联调验证,确认DSMC Local Bus链路能够稳定建立,并在512B、8-

2026-04-16

OpenClaw秒级上线!JishuShell适配米尔RK3576开发板

随着端侧AI从“实验室探索”迈向量产化,“效率”成为了产业落地的生命线。米尔电子联合安谋科技(Arm China)极术社区,通过硬件与软件工具链的深度协同,正式推出了“MYD-LR3576核心板+JishuShell”一体化部署方案。该方案让备受关注的端侧AI Agent——OpenClaw在边缘侧的部署门槛降至冰点。步入2026年,大模型技术的竞争重心正从云端参数规模向端侧应用落地转移。端侧AI

2026-04-10

米尔RK3576 + ROS2 进阶:NPU加速MixFormerV2目标跟随与机械臂抓取实战

回顾上篇:基于RK3576+ROS2 Humble+SLAM Toolbox+Nav2,我们实现了机器人的建图与自主导航。机器人已经能够“走到哪里”。但真正的智能机器人不仅要“走到哪”,还要“看到并操作”——识别特定物体、主动跟随、近距离抓取。本文将在此基础上,集成深度摄像头,实现机器人核心功能:使用米尔RK3576 NPU加速MixFormerV2进行目标跟踪,替代传统OpenCV算法;移动底盘

2026-04-10

智造新方向 · 国产芯未来,米尔即将亮相新唐2026研讨会

在全球绿色能源与智能制造浪潮推动产业升级的当下,半导体技术的创新正持续为各领域发展注入核心动力。为深化产业技术交流、携手共探国产芯发展新机遇,新唐科技携手芯唐南京将于2026年4月14日至5月28日在全国城市巡回举办年度研讨会 ——“智造新方向・国产芯未来”。米尔电子作为新唐的合作伙伴,将携米尔基于新唐MA35D1核心板开发板及解决方案,亮相0417深圳、0421南京、0423北京等场次的研讨会。

2026-04-02

当6 TOPS不再是极限:RK3576+Hailo-8,让高帧率摄像头真正“实时”

在边缘计算领域,算力与实时性之间的博弈从未停止。近期基于米尔MYD-LR3576 开发板+PCIe M.2接口Hailo-8算力卡进行了一系列深度测试,一组实测数据,或许能帮你重新审视边缘AI的“性能天花板”。图:米尔基于RK3576开发板一、RK3576 的算力极限在哪里?RK3576内置NPU由2核组成,具备6 TOPS 算力,在常规轻量级模型推理中表现不俗。但在实际项目中,我们通过多路并发测

2026-03-27

新品!从MINI到工业板:米尔T153开发板工业场景全覆盖

今年1月,米尔发布了MYD-YT153MX-MINI开发板,该产品精准切入国产核心板在中端市场领域,具有极致性价比,自上市即获得良好的市场反响。为方便开发者灵活选择、适配更专业的场景,米尔电子正式推出基于同款全志T153四核异构工业处理器的MYD-YT153MX工业开发板,两款开发板形成完整组合,下面来详细介绍工业开发板的不同之处。工业开发板——为严苛场景而生工业开发板:定位工业应用开发与评估,接

2026-03-19

新品!瑞萨RZ/T2H驱控一体单芯、多轴实时控制,助力工业以太网

米尔电子发布基于瑞萨高端MPU处理器RZ/T2H的CPU模组-MYC-YT2HX核心板及开发板。该产品在前代产品RZ的基础上进行了全面升级,RZ/T2H以其强大的硬件支持、全面的软件开发工具、丰富的工业以太网协议和安全解决方案,以及多操作系统的灵活配置,为客户提供了一个全方位、高效率的开发环境。MYC-YT2HX核心板的推出,旨在解决工业数字化进程中对高性能产品升级以及对复杂网络控制的需求,如工业

2026-03-12

RK3576 + ROS2 SLAM建图与导航实战

前言文档定位与目标读者本文档面向具备一定ROS基础、希望深入理解并在实际项目中部署ROS2 Humble + SLAM Toolbox + Nav2完整建图与导航系统的机器人工程师。我们将从零开始,基于米尔RK3576开发板逐步构建一个功能完备的自主移动机器人系统,涵盖环境搭建、机器人建模、SLAM建图、自主导航以及生产级系统的优化与排错。为什么选择SLAM Toolbox + Nav2?在ROS

2026-03-12

米尔亮相德国嵌入式展2026 Embedded World

2026年3月10日,全球嵌入式系统领域的年度盛会——Embedded World在德国纽伦堡展览中心盛大启幕。作为领先的嵌入式处理器模组厂商,米尔电子携全系列嵌入式核心板、开发板及创新解决方案重磅亮相,与来自全球40多个国家的1100余家展商、32000余名专业观众共赴这场技术盛宴。Embedded World自创办以来,已成为全球规模最大、影响力最深远的嵌入式系统展览会,聚焦嵌入式硬件系统、软